#### DISSERTATION

# AUTOMATING THE DERIVATION OF MEMORY ALLOCATIONS FOR ACCELERATION OF POLYHEDRAL PROGRAMS

Submitted by

Corentin Ferry

Department of Computer Science

In partial fulfillment of the requirements

For the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Spring 2024

#### Doctoral Committee:

Advisor: Sanjay Rajopadhye Co-Advisor: Steven Derrien

Jesse Wilson Sudeep Pasricha Jedidiah McClurg Ponnuswamy Sadayappan Florent de Dinechin Caroline Collange Copyright by Corentin Ferry 2024 All Rights Reserved

#### ABSTRACT

# AUTOMATING THE DERIVATION OF MEMORY ALLOCATIONS FOR ACCELERATION OF POLYHEDRAL PROGRAMS

As processors compute power keeps increasing, so do their demands in memory accesses: some computations will require a higher bandwidth and exhibit regular memory access patterns, others will require a lower access latency and exhibit random access patterns. To cope with all demands, memory technologies are becoming diverse. It is then necessary to adapt both programs and hardware accelerators to the memory technology they use. Notably, memory access patterns and memory layouts have to be optimized. Manual optimization can be extremely tedious and does not scale to a large number of processors and memories, where automation becomes necessary.

In this Ph.D dissertation, we suggest several automated methods to derive data layouts from programs, notably for FPGA accelerators. We focus on getting the best throughput from high-latency, high-bandwidth memories and, for all kinds of memories, the lowest redundancy while preserving contiguity. To this effect, we introduce mathematical analyses to partition the data flow of a program with uniform and affine dependence patterns, propose memory layouts and automation techniques to get optimized FPGA accelerators.

### TABLE OF CONTENTS

| ABSTRACT  | Γ                                                                   | ii |

|-----------|---------------------------------------------------------------------|----|

|           | ABLES                                                               | iv |

|           | IGURES                                                              | V  |

| Chapter 1 | Résumé en français                                                  | 1  |

| 1.1       | Introduction                                                        | 1  |

| 1.2       | Allocation de données contigue pour pavage rectangulaire            | 3  |

| 1.3       | Analyse et découpage du flot de données                             | 4  |

| 1.4       | Allocation de données partitionnée et compression à la volée        | 4  |

| 1.5       | Extension aux dépendances affines                                   | 5  |

| Chapter 2 | Introduction                                                        | 7  |

| 2.1       | A need for further memory optimizations                             | 8  |

| 2.1.1     | An increasing pressure on memory due to parallelism                 | 8  |

| 2.1.2     | A widening space of memory architectures                            | 10 |

| 2.1.3     | Bandwidth-bound FPGA accelerators                                   | 12 |

| 2.1.4     | Recent improvements in the utilization of memory subsystems         | 13 |

| 2.1.5     | Application-specific data layouts increase bandwidth utilization    | 16 |

| 2.1.6     | The case for automation of memory layout optimizations              | 17 |

| 2.2       | Contributions of this Ph.D                                          | 18 |

| 2.2.1     | A multi-level contiguous memory layout for rectangular tiles        | 19 |

| 2.2.2     | An irredundant, atomic partitioning of inter-tile communications    |    |

|           | for arbitrary tile shapes                                           | 19 |

| 2.2.3     | A compressed and contiguous memory layout for arbitrary tile shapes | 19 |

| 2.2.4     | An extension of the data flow partitioning to affine dependences .  | 20 |

| Chapter 3 | Background                                                          | 21 |

| 3.1       | Locality and performance                                            | 21 |

| 3.1.1     | Roofline model                                                      | 21 |

| 3.1.2     | Access locality                                                     | 23 |

| 3.2       | Memory architectures and transfers                                  | 23 |

| 3.2.1     | High-bandwidth controller features                                  | 24 |

| 3.3       | High-level synthesis                                                | 26 |

| 3.3.1     | From $C/C++$ to an architecture                                     | 26 |

| 3.3.2     | Memory accesses in HLS                                              | 30 |

| 3.4       | Polyhedral model and tiling                                         | 32 |

| 3.4.1     | Abstractions                                                        | 32 |

| 3.4.2     | Modelling Dependences                                               | 34 |

| 3.4.3     | Tiling                                                              | 35 |

| 3.4.4     | Notations                                                           | 39 |

| 3.5       | Polyhedral compilation and accelerator synthesis                    | 39 |

| 3.5.1     | Extracting parallelism within the polyhedral model                   | 41  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------|-----|--|--|--|--|--|

| 3.5.2     | From a parallel polyhedral representation to a parallel architecture | 42  |  |  |  |  |  |

| 3.5.3     | From a polyhedral representation to a memory access pattern          | 44  |  |  |  |  |  |

| Chapter 4 | A Multi-level Contiguous Data Allocation for Rectangular Tiles       | 46  |  |  |  |  |  |

| 4.1       | Introduction                                                         |     |  |  |  |  |  |

| 4.2       | Related work                                                         |     |  |  |  |  |  |

| 4.2.1     | Improving temporal locality                                          | 48  |  |  |  |  |  |

| 4.2.2     | Increasing the effective bandwidth                                   | 49  |  |  |  |  |  |

| 4.2.3     | Automatic synthesis of optimized hardware                            | 52  |  |  |  |  |  |

| 4.3       | Canonical Facet Allocation                                           | 53  |  |  |  |  |  |

| 4.3.1     | Description of the method                                            | 53  |  |  |  |  |  |

| 4.3.2     | Hypotheses                                                           | 54  |  |  |  |  |  |

| 4.3.3     | Definitions                                                          | 55  |  |  |  |  |  |

| 4.3.4     | Multi-projection: contiguity along multiple directions               | 56  |  |  |  |  |  |

| 4.3.5     | Flow-in from first-level neighbors: Full-tile contiguity             | 62  |  |  |  |  |  |

| 4.3.6     | Flow-in from second-level neighbors: Inter-tile contiguity           | 65  |  |  |  |  |  |

| 4.3.7     | Contiguity of flow-in from third-level neighbors                     | 68  |  |  |  |  |  |

| 4.3.8     | Case of $k$ -th level neighbors                                      | 69  |  |  |  |  |  |

| 4.4       | Implementation                                                       | 69  |  |  |  |  |  |

| 4.4.1     | Overview: compiler pass                                              | 69  |  |  |  |  |  |

| 4.4.2     | Determining the facets and their layout                              | 70  |  |  |  |  |  |

| 4.4.3     | Copy-in/out code generation                                          | 70  |  |  |  |  |  |

| 4.4.4     | Generating HLS code                                                  | 75  |  |  |  |  |  |

| 4.5       | Evaluation                                                           | 76  |  |  |  |  |  |

| 4.5.1     | Experimental protocol                                                | 76  |  |  |  |  |  |

| 4.5.2     | Results and discussion                                               | 78  |  |  |  |  |  |

| 4.6       | Conclusion                                                           | 82  |  |  |  |  |  |

| Chapter 5 | Maximal Atomic irRedundant Sets: a Usage-based Dataflow Partition-   |     |  |  |  |  |  |

|           | ing Algorithm                                                        | 85  |  |  |  |  |  |

| 5.1       | Introduction                                                         | 85  |  |  |  |  |  |

| 5.2       | Related Work                                                         | 86  |  |  |  |  |  |

| 5.3       | MARS: Maximal Atomic irRedundant Sets                                | 86  |  |  |  |  |  |

| 5.3.1     | Notations and hypotheses                                             | 87  |  |  |  |  |  |

| 5.3.2     | Definition                                                           | 87  |  |  |  |  |  |

| 5.3.3     | Computation                                                          | 88  |  |  |  |  |  |

| 5.3.4     | Dual view: flow-in                                                   | 95  |  |  |  |  |  |

| 5.4       | Implementation and Analysis                                          | 95  |  |  |  |  |  |

| 5.4.1     | MARS procedure implementation                                        | 96  |  |  |  |  |  |

| 5.4.2     | Handling multi-statement programs                                    | 96  |  |  |  |  |  |

| 5.4.3     | Results                                                              | 99  |  |  |  |  |  |

| 5.5       | Applications and Future Directions                                   | 103 |  |  |  |  |  |

| 5.5.1     | Memory allocation, Compression                                       | 103 |  |  |  |  |  |

| 5.5.2     | Error detection                                                      | 103 |  |  |  |  |  |

| 5.5.3     | A case for merging MARS                                             | 104 |

|-----------|---------------------------------------------------------------------|-----|

| 5.6       | Conclusion                                                          | 104 |

| Chapter 6 | An Irredundant and Compressed Data Layout to Optimize Bandwidth     |     |

| -         | Utilization of FPGA Accelerators                                    | 106 |

| 6.1       | Motivation                                                          | 107 |

| 6.1.1     | Illustrative example: 1D Jacobi stencil                             | 108 |

| 6.1.2     | Padding, packing and compression                                    | 110 |

| 6.1.3     | Contributions                                                       | 112 |

| 6.2       | Related Work                                                        | 113 |

| 6.2.1     | Data Compression                                                    | 113 |

| 6.2.2     | Memory access optimization                                          | 114 |

| 6.3       | Memory allocation for FPGA accelerator                              | 116 |

| 6.3.1     | Extracting Contiguous Data Blocks                                   | 116 |

| 6.3.2     | Enabling Coalesced Accesses across Contiguous Data Blocks           | 117 |

| 6.3.3     | Contiguity-Preserving Block Compression                             | 123 |

| 6.4       | Implementation and Analysis                                         | 125 |

| 6.4.1     | Simplification of polyhedral control flow on FPGA                   | 125 |

| 6.4.2     | From MARS to Collect/Dispatch Functions                             | 127 |

| 6.4.3     | Automatic compression                                               | 128 |

| 6.5       | Evaluation                                                          | 130 |

| 6.5.1     | Protocol and benchmarks                                             | 131 |

| 6.5.2     | Results and discussion                                              | 132 |

| 6.6       | Conclusion                                                          | 140 |

| Chapter 7 | An Irredundant Decomposition of Data Flow with Affine Dependences . | 141 |

| 7.1       | Introduction                                                        | 141 |

| 7.2       | Motivation                                                          | 142 |

| 7.2.1     | Necessity of spatial locality                                       | 142 |

| 7.2.2     | Limitations of existing transformations                             | 143 |

| 7.3       | Background and hypotheses                                           | 144 |

| 7.3.1     | Polyhedral representation, tiling                                   | 144 |

| 7.3.2     | Linear algebra                                                      | 146 |

| 7.4       | Partitioning Data and Iteration Spaces                              | 147 |

| 7.4.1     | Case of uniform dependences                                         | 148 |

| 7.4.2     | The problem: uniform versus affine dependences                      | 148 |

| 7.4.3     | Case of a single affine dependence                                  | 149 |

| 7.4.4     | Case of multiple, uniformly intersecting dependences                | 158 |

| 7.4.5     | Case of multiple, non-uniformly intersecting dependences            | 162 |

| 7.4.6     | Case of dependences between tiled spaces                            | 168 |

| 7.5       | Related work                                                        | 170 |

| 7.5.1     | Goal of partitioning                                                | 170 |

| 7.5.2     | Partitioning methods                                                | 171 |

| 7.6       | Conclusion                                                          | 172 |

| Chapter 8    | Conclusions and perspectives                 |

|--------------|----------------------------------------------|

| 8.1          | Conclusions                                  |

| 8.2          | Perspectives                                 |

| 8.2.1        | On the polyhedral compilation aspect         |

| 8.2.2        | On using more hardware properties            |

| 8.2.3        | On use cases of polyhedral-based allocations |

| Publications | and Contributions                            |

### LIST OF TABLES

| 2.1        | Benchmark figures of various memory technologies (DDR4, HBM) and platforms (U280 board, Amazon F1 datacenter platform)                                                                         | 11         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1<br>3.2 | Notations used throughout this document                                                                                                                                                        | 40<br>41   |

| 4.1        | Benchmarks used for testing CFA. Equivalent applications have the same computational dependence pattern as the benchmark and would show similar performance                                    | . 77       |

| 5.1<br>5.2 | Results obtained from the MARS procedure. $\#$ CT = number of consumer tiles; $\#$ MARS = number of MARS; $\#$ Singl. = number of MARS of cardinality 1 Computation time for MARS over 10 runs | 100<br>100 |

| 6.1        | Characteristics of the selected benchmarks. The number of bursts per tile accounts for layout-induced access coalescing and is independent of tile and problem size                            | 130        |

| 6.2        | Layout Computation and Code Generation Time                                                                                                                                                    | 136        |

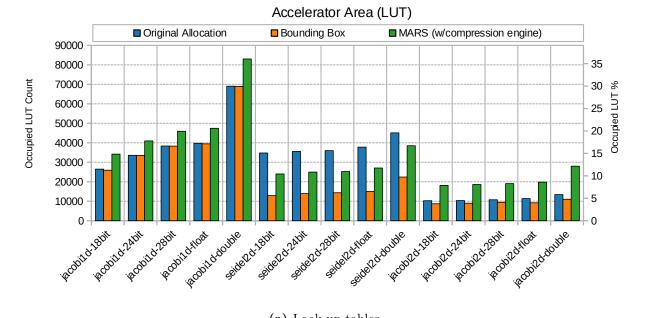

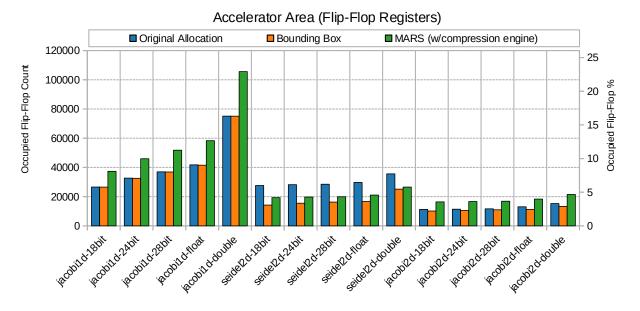

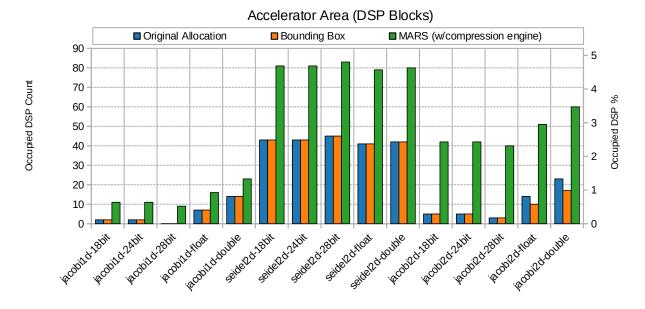

| 6.3        | Occupied area for jacobi-2d, tile size 10x10x10. MARS versions contain a                                                                                                                       |            |

|            | scratchpad memory for 11520 compression metadata                                                                                                                                               | 137        |

### LIST OF FIGURES

| 3.1  | Roofline model                                                                                              | 22 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Burst accesses span over multiple addresses in a single transaction, amortizing                             |    |

|      | the transaction latency over all elements accessed                                                          | 25 |

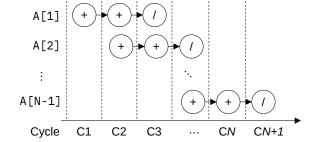

| 3.3  | Loop unrolling in HLS creates parallel operators, and executes the loop iterations                          |    |

|      | in parallel provided they are independent                                                                   | 28 |

| 3.4  | Loop pipelining in HLS overlaps multiple iterations of a loop, starting a new                               |    |

|      | iteration every II cycles (here II=1), provided there is no dependence between                              |    |

|      | them                                                                                                        | 28 |

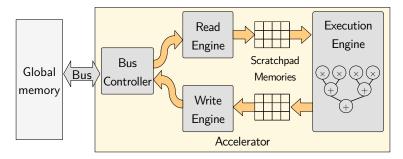

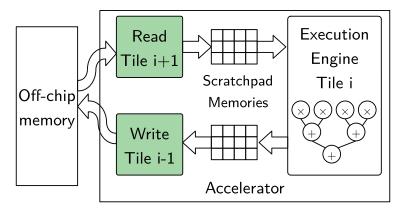

| 3.5  | Task-level structure of an accelerator: read, execution and writeback happen                                |    |

|      | separately                                                                                                  | 29 |

| 3.6  | Changing layouts is necessary to get both contiguity and parallelism                                        | 32 |

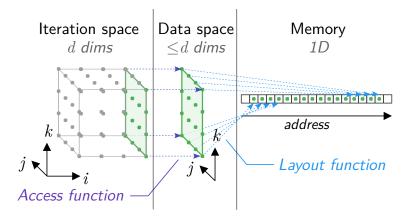

| 3.7  | Iteration and data spaces in the classical polyhedral model. A memory map gives                             |    |

|      | each data space point an address                                                                            | 34 |

| 3.8  | Rectangular tiling (cutting with a family of hyperplanes $\mathcal{H}_i: i=4k, k \in \mathbf{N}$ and        |    |

|      | $\mathcal{H}_t: t=3p, p \in \mathbf{N}$ ) is illegal on the left, and becomes legal on the right after time |    |

|      | skewing                                                                                                     | 36 |

| 3.9  | Rectangular tiling applied to two dimensions of a loop nest                                                 | 37 |

| 3.10 | Flow-out set of a tile with a Smith-Waterman dependence pattern. Dependences                                |    |

|      | pointing to other tiles are shown producer to consumer:                                                     | 39 |

| 3.11 | Macro-pipeline structure: read-execute-write. Our contribution focuses on the                               |    |

|      | read and write stages                                                                                       | 44 |

| 4.1  | The method proposed in this work improves spatial locality, giving access to                                |    |

| 1.1  | higher performance due to fewer memory-induced stalls                                                       | 47 |

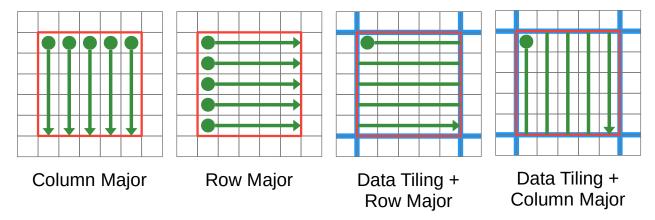

| 4.2  | Memory layouts (non-tiled and tiled) for a 2-dimensional data space, and access pat-                        | 11 |

| 1.2  | terns for a tile. Each dot is the start of a burst access, that spans until the arrow tip.                  |    |

|      | Data tiling layouts enable a single burst access per tile instead of one per row/column.                    | 51 |

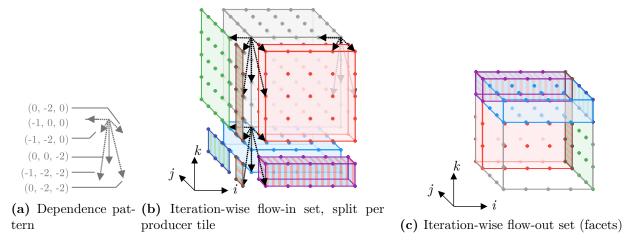

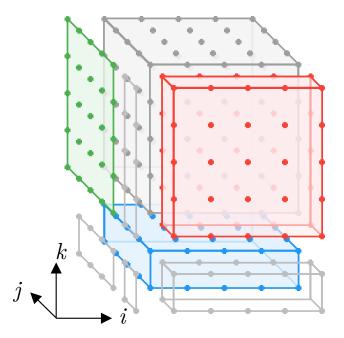

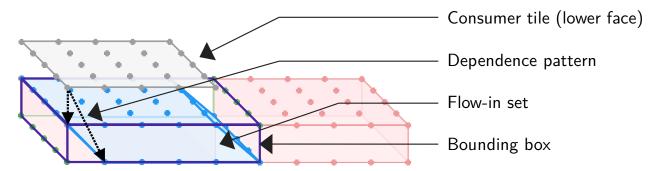

| 4.3  | An instance of flow-in and flow-out sets. The flow-out set is the union of thicker                          | -  |

|      | versions of the tile faces (facets), while the flow-in set is composed of an union                          |    |

|      | of either whole or partial facets. Some flow-in sets are adjacent in the iteration                          |    |

|      | space; CFA reflects this adjacency in memory                                                                | 54 |

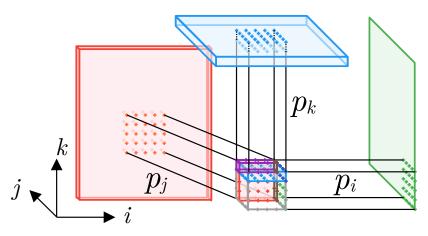

| 4.4  | Multi-projection: each facet (see Figure 4.3c) is projected (mapped) to a data space.                       |    |

|      | Choice of contiguity comes later on                                                                         | 57 |

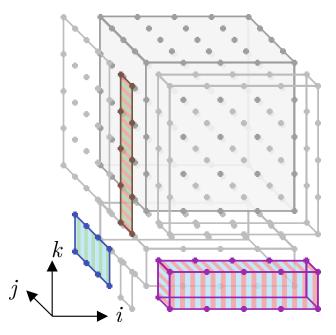

| 4.5  | First-level neighbor facets that are consumed by the grey tile                                              | 63 |

| 4.6  | Flow-in iterations from second-level neighbors of an iteration tile. CFA places in mem-                     |    |

|      | ory each data tile containing a slab next to a fully consumed data tile to read both in                     |    |

|      | the same burst                                                                                              | 66 |

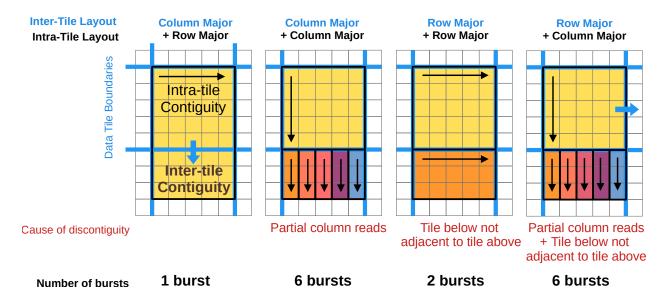

| 4.7  | The four possible data layouts for a 2-dimensional array in tiled data layout (inter-tile                   |    |

|      | + intra-tile layouts), and the number of bursts needed to read a tile and part of the                       |    |

|      | tile below it. Only one layout allows a single burst spanning both tiles                                    | 66 |

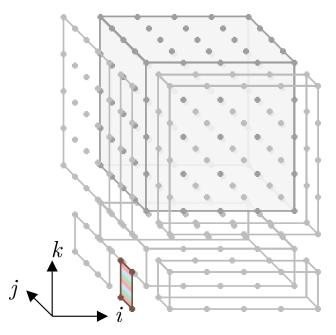

| 4.8   | Flow-in from third-level neighbor (pattern of Figure 4.3. CFA places these four points contiguously in memory within a data tile (intra-tile contiguity) | 68  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

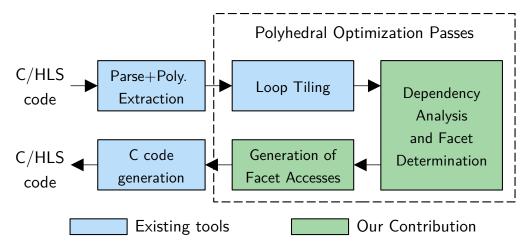

| 4.9   | Polyhedral compiler flow including the CFA pass (shown broken into two)                                                                                  | 70  |

| 4.10  | Taking a rectangular over-approximation of the actual flow-in set incurs redundant                                                                       | • • |

|       | reads. Contiguous data (facets) are in red: an over-approximation may be necessary                                                                       |     |

|       | to preserve access contiguity                                                                                                                            | 74  |

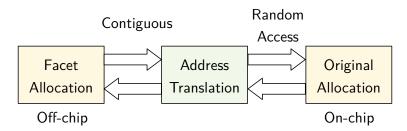

| 4.11  | Merger of two loops from which a burst access is inferred. On-chip addresses are                                                                         |     |

|       | random, while off-chip addresses are consecutive                                                                                                         | 75  |

| 4.12  | Top-level function, assuming tile size is TS, local memories are TS <sup>2</sup> big and the iteration                                                   |     |

|       | space is TS <sup>3</sup> . Such sizes are typical of iterative stencils                                                                                  | 76  |

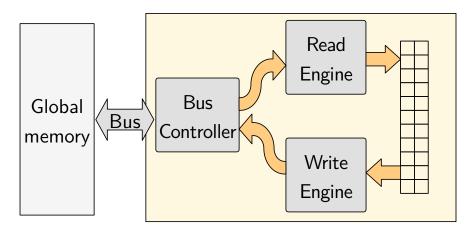

| 4.13  | Memory-bound accelerator used for benchmarking: only the read and write engines are                                                                      |     |

|       | implemented                                                                                                                                              | 77  |

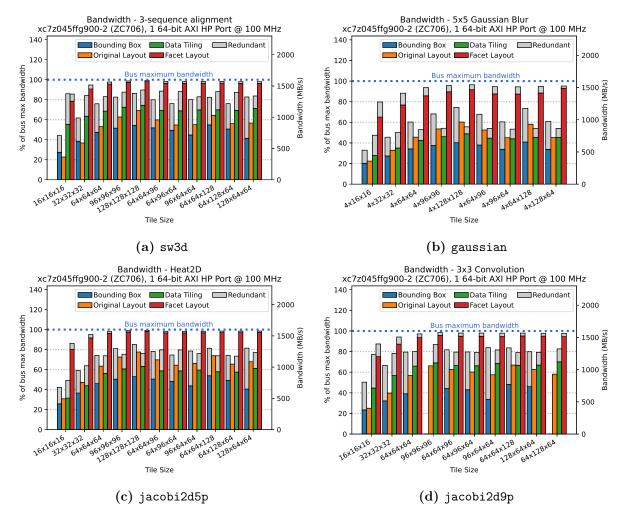

| 4.14  | Bandwidth for all baselines, per benchmark. CFA is efficient even for tiles where one                                                                    |     |

|       | dimension is much smaller than the others. Bounding box is the technique used by                                                                         |     |

|       | Pouchet et al. [60], Data Tiling is used by Ozturk et al. [58], and the original layout is                                                               |     |

| 4 1 5 | the best-effort baseline as in Bayliss et al. [5]                                                                                                        | 79  |

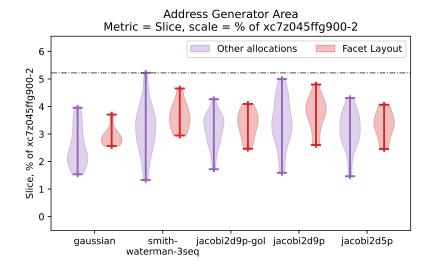

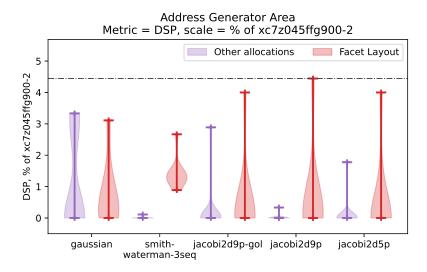

| 4.15  | 1 0                                                                                                                                                      | റ   |

| 1 16  | available area of xc7z045ffg900-2. The vertical lines span from minimum to maximum.                                                                      | 83  |

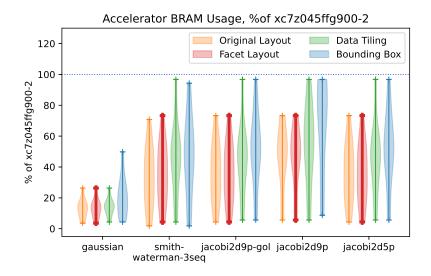

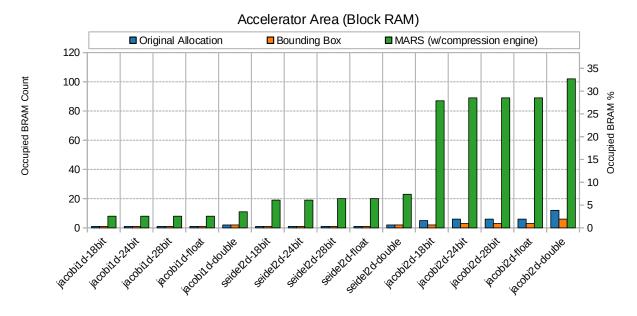

| 4.10  | BRAMs occupied by all baselines (in color), for each benchmark, as a percentage of xc7z045ffg900-2 BRAMs                                                 | 84  |

|       | xcrzu45iig900-2 brams                                                                                                                                    | 04  |

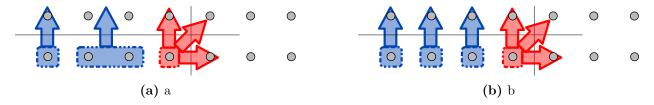

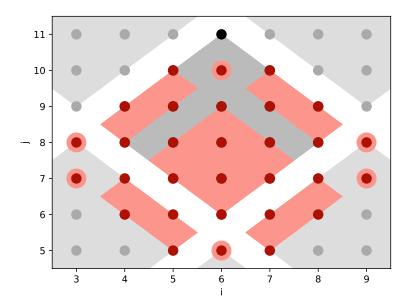

| 5.1   | Sets of iterations for Smith-Waterman matching single-producer, atomicity prop-                                                                          |     |

|       | erties, but not maximality. Maximality forces the search for a non-trivial solution                                                                      | 88  |

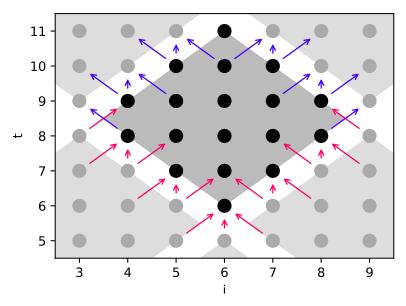

| 5.2   | Flow-out set for a skewed tile of a Smith-Waterman kernel. The arrows corre-                                                                             |     |

|       | spond to the dependence pattern (PRDG)                                                                                                                   | 89  |

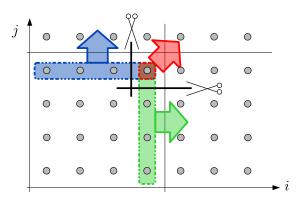

| 5.3   | Flow-out set of a tile intersected with each consumers tile's flow-in set. The                                                                           |     |

|       | breakup we propose, illustrated by scissors, splits iterations that have different                                                                       |     |

| ٠,    | consumer tiles.                                                                                                                                          | 91  |

| 5.4   | MARS and their consumers for Smith-Waterman using square tiling                                                                                          | 93  |

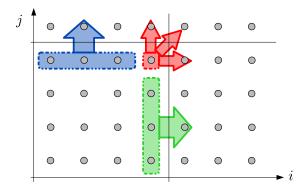

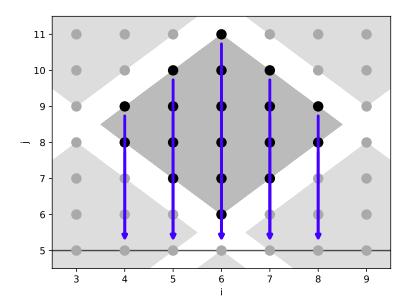

| 5.5   | Visualization of MARS generated using the MARS calculator                                                                                                | 101 |

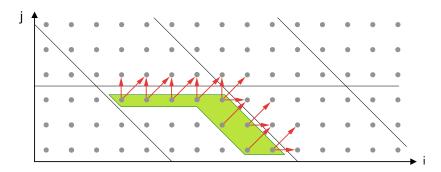

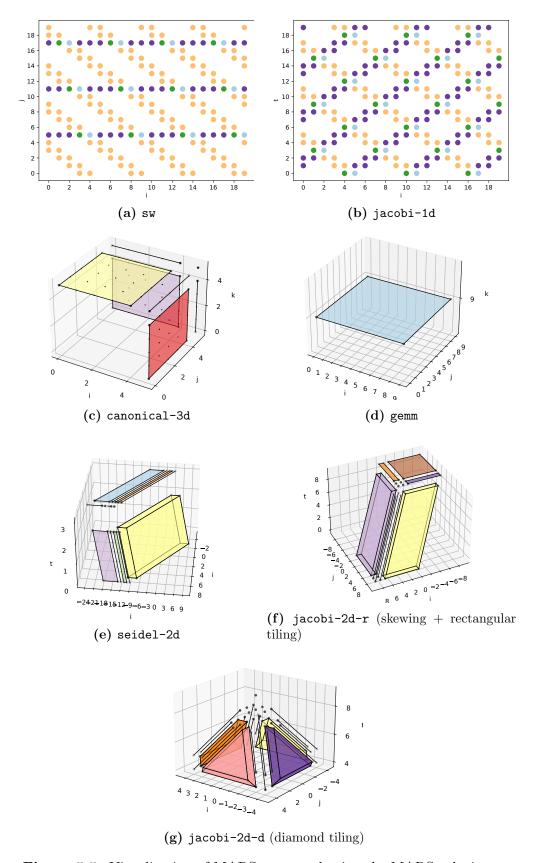

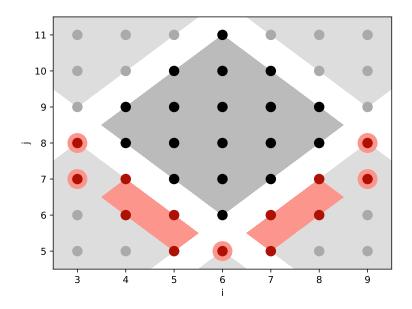

| 6.1   | Domain of the Jacobi stencil divided into tiles of size $6 \times 6$ . Each tile contains 18                                                             |     |

| 0     | $(t,i)$ points corresponding to 18 computations of $c_{t,i}$ s                                                                                           | 109 |

| 6.2   | Inter-tile communication pattern for the Jacobi stencil: red arrows indicate data                                                                        |     |

|       | input into the tile shown in the center, and blue arrows indicate data output from                                                                       |     |

|       | this tile                                                                                                                                                | 109 |

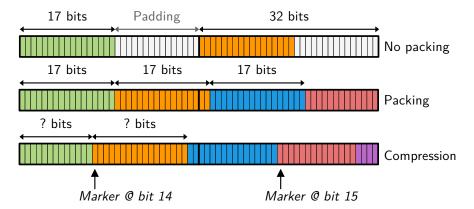

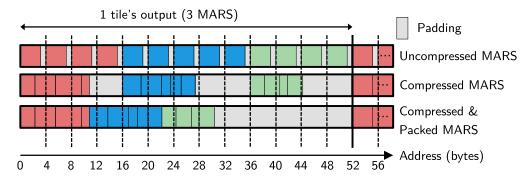

| 6.3   | Data packing and compression reduce storage and transfer redundancy at the                                                                               |     |

|       | expense of address alignment and, for compression, predictability of addresses                                                                           | 110 |

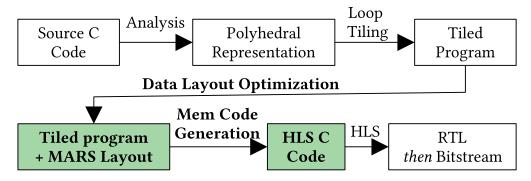

| 6.4   | Compiler flow (contributions of this chapter in green)                                                                                                   | 113 |

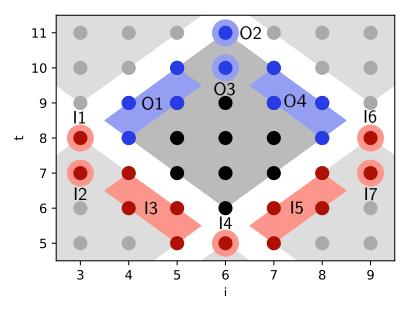

| 6.5   | MARS: Groups of points within a tile which data is contiguous in global memory.                                                                          |     |

|       | In blue, the MARS produced by the center tile (O1 to O4); in red, the MARS                                                                               |     |

|       | consumed by that same tile (I1 to I7)                                                                                                                    | 116 |

| 6.6   | MARS data shown without compression, with compression (inside the MARS)                                                                                  |     |

|       | and with MARS compression and packing. Packing the compressed MARS pre-                                                                                  | 100 |

|       | serves the contiguity of coalesced accesses                                                                                                              | 123 |

| 6.7  | Structure of the MARS dispatch implementation (off-chip to on-chip layout)                              | 128  |

|------|---------------------------------------------------------------------------------------------------------|------|

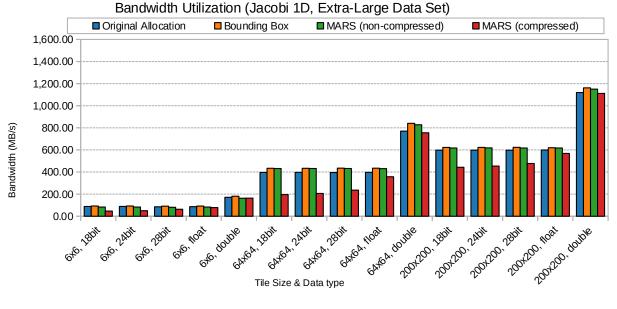

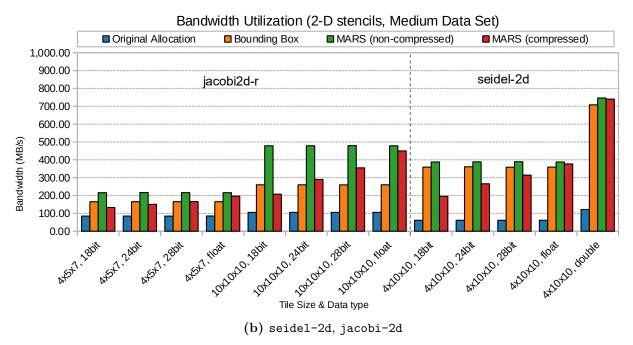

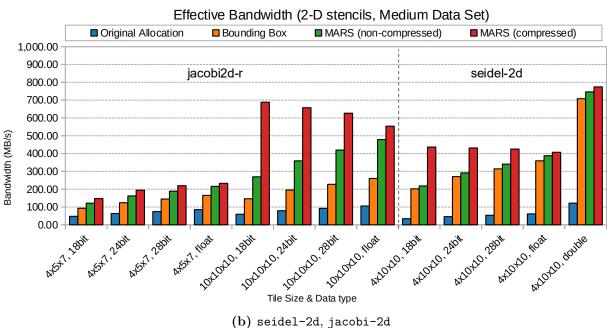

| 6.8  | Bandwidth utilization as seen from outside the accelerator                                              | 133  |

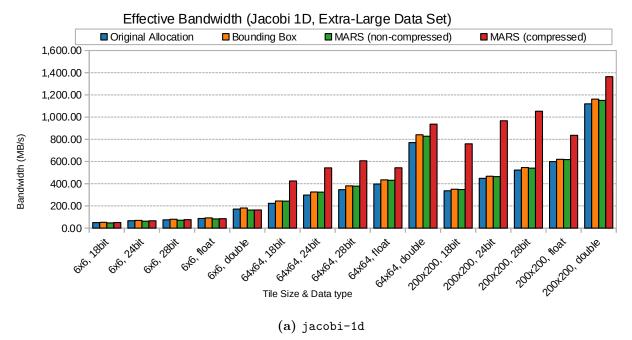

| 6.9  | Effective bandwidth: bandwidth after decompression, minus redundancy                                    | 134  |

| 6.10 | Area statistics for the three benchmarks. Tile sizes are $200 \times 200$ for jacobi1d,                 |      |

|      | $10 \times 10 \times 10$ for jacobi2d and $4 \times 10 \times 10$ for seidel2d                          | 139  |

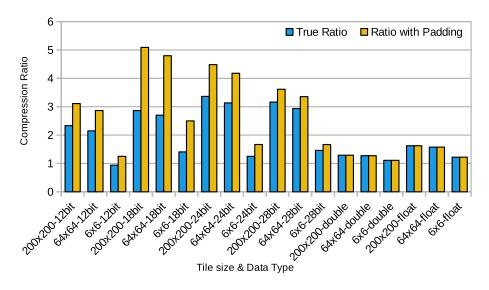

| 6.11 | Compression ratio vs. data type and tile size for jacobi1d                                              | 140  |

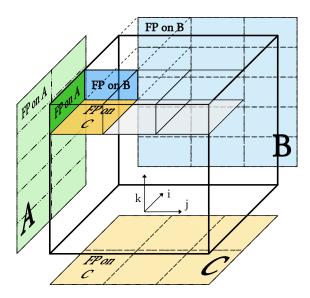

| 7.1  | Tiled matrix product, and footprint of a tile on the matrices. Each footprint                           |      |

|      | "patch" is composed of multiple contiguous rows or columns, but none of the                             |      |

|      | patches are entirely contiguous in memory                                                               | 143  |

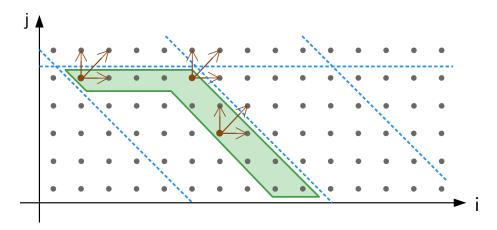

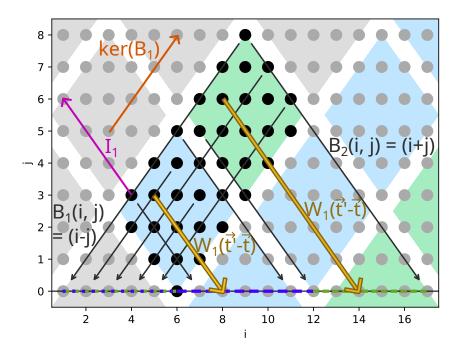

| 7.2  | Footprint of one tile with a single affine dependence $B(i,j) = (i)$ . The one-                         |      |

|      | dimensional destination space is shown as a continuous line                                             | 151  |

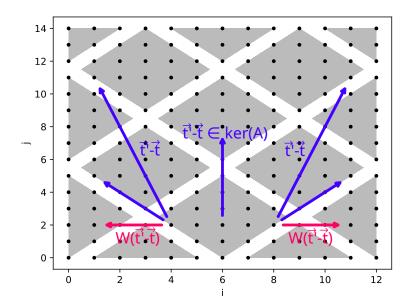

| 7.3  | Some consumer tiles of one tile $T(\vec{t})$ with a single dependence $B(i,j)=(i)$ , and                |      |

| ,    | the projection $W(\vec{t'}-\vec{t})$ on a supplementary of $\ker(A)$ . There are a finite number        |      |

|      | of such projected vectors, and they are constant                                                        | 151  |

| 7.4  | MARS obtained with a single affine dependence $B(i,j) = (i)$                                            | 154  |

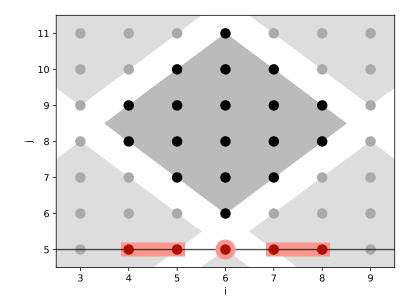

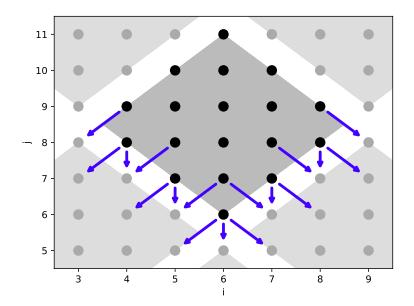

| 7.5  | Flow-in dependences of tile $T(\vec{t})$ with uniformly intersecting dependences (Jacobi                | 104  |

| 1.0  |                                                                                                         | 161  |

| 76   | 1D)                                                                                                     | 161  |

| 7.6  | Consumer tiles of array $\mathcal{A}$ with Jacobi 1D dependences, sharing their footprint               | 1.00 |

|      | with tile $T(\vec{t})$                                                                                  | 162  |

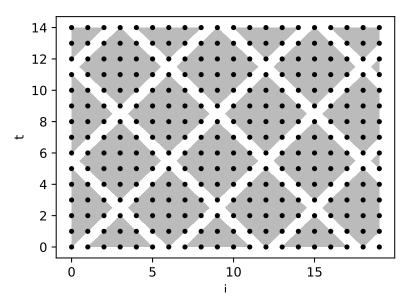

| 7.7  | MARS for uniformly intersecting dependences (Jacobi 1D)                                                 | 163  |

| 7.8  | Coincidence between MARS computed with the uniform dependence method,                                   |      |

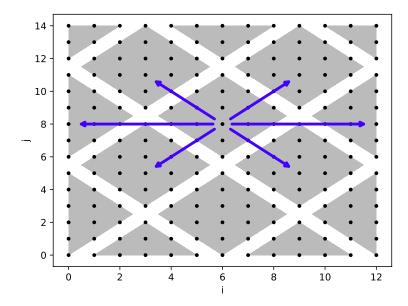

|      | and those computed with the affine method                                                               | 163  |

| 7.9  | Non-uniformly intersecting dependences do not guarantee that the vectors $W_i(\vec{t'}-$                |      |

|      | $\vec{t}$ ) do not depend on $\vec{t}$ , i.e. each tile's footprint is not necessarily a translation of |      |

|      | another tile's footprint                                                                                | 165  |

# Chapter 1

# Résumé en français

### 1.1 Introduction

Dans le domaine du calcul haute performance comme dans celui de l'informatique embarquée, on observe une demande croissante de performance de calcul combinée à une demande de réduction de la consommation énergétique des mêmes systèmes. Pour parvenir à ces fins, il est nécessaire d'utiliser des accélérateurs matériels et des architectures spécifiques.

L'accent mis sur le parallélisme au cours des années 2010 est à l'origine d'une importante proportion des gains en performance observés durant cette décennie. Celle-ci fut permise à la fois par la finesse de gravure des puces, qui permit de mettre davantage de ressources de calcul à disposition des utilisateurs, et par le développement de compilateurs auto-parallélisants, qui en permirent l'exploitation.

L'augmentation de la puissance de calcul se traduit par une pression accrue sur les systèmes mémoires qui, incapables d'y satisfaire, ralentissent alors les calculs. Ils sont aussi à l'origine d'une fraction importante de la consommation énergétique en raison des transferts inter-puces qu'ils effectuent. Pour faire face à ces deux défis, de nouvelles architectures mémoire sont en développement : certaines, comme les mémoires LPDDR, visent une basse consommation; d'autres au contraire cherchent à maximiser le débit en entrée et sortie comme les architectures HBM.

L'émergence de nouvelles architectures mémoire permet d'adapter le choix du soussystème mémoire au système développé. Ce seul choix ne suffit pas à garantir un débit effectif ni une consommation optimales. Afin d'exploiter au mieux l'architecture choisie, il est nécessaire d'optimiser le programme ou l'architecture de calcul afin d'optimiser son utilisation de la mémoire. On peut regrouper les optimisations existantes en deux catégories : les optimisations de localité, qui visent à réduire la quantité d'entrée/sortie mémoire en exploitant les données présentes dans les caches et mémoires locales, et les optimisations d'accès, qui visent à réduire le temps de transfert total et ainsi obtenir le débit le plus élevé possible.

Dans cette thèse de doctorat, on s'intéresse particulièrement aux optimisations d'accès. Contrairement aux optimisations de localité, dont beaucoup sont aujourd'hui automatisées, les optimisations d'accès sont peu nombreuses, et demandent des modifications profondes dans la structure des données utilisées par le programme. De telles modifications peuvent permettre d'exhiber des motifs d'accès à la mémoire plus efficaces, car plus adaptés à la topologie des mémoires et au fonctionnement des contrôleurs. Notamment, les accès contigus, ou burst, sont les plus efficaces avec les contrôleurs DDR, mais aussi les plus difficiles à faire apparaître.

On développe dans cette thèse des méthodes d'analyse de programme permettant de connaître les besoins précis en données de chaque partie accélérée du programme, et de transformer la disposition des données ainsi que les motifs d'accès de l'accélérateur pour faire apparaître des accès contigus. Pour effectuer de telles modifications, rendant potentiellement inintelligibles les données à l'utilisateur, il est nécessaire de s'assurer de la correction des résultats fournis par le programme; cette assurance n'est possible que moyennant des hypothèses sur le comportement du programme, qui sont vérifiées à la compilation. Afin de permettre de transformer l'éventail le plus large possible de programmes, on cherche dans cette thèse quelles sont les hypothèses les plus faibles permettant de garantir la correction des transformations effectuées.

On propose ainsi dans cette thèse les contributions qui suivent :

- Une allocation de données contigue pour programmes utilisant un pavage polyédrique rectangulaire permettant aux accès contigus de traverser les frontières des tuiles,

- Une analyse à grain fin du flot de données du programme ainsi qu'un découpage de celui-ci en blocs de données pouvant être rendus contigus,

- Une transformation de programme utilisant l'analyse précédente pour compresser à la volée les données tout en assurant un volume d'entrée/sortie minimal,

- Une étude théorique sur les limites de validité des transformations proposées.

# 1.2 Allocation de données contigue pour pavage rectangulaire

Dans le chapitre 4, on propose une allocation de données spécifique aux accélérateurs FPGA visant à maximiser l'exploitation de la contiguité tout en contrôlant le volume d'accès dits *redondants*, c'est-à-dire le volume de données échangées bien que non utilisées afin de préserver la contiguité.

Lorsque le programme admet une représentation polyédrique, il peut être possible de lui appliquer un pavage (découpage de l'espace des itérations en tuiles de forme similaire), afin d'augmenter la localité des accès. Des données issues de l'exécution de chaque tuile sont nécessaires pour exécuter d'autres tuiles voisines; en outre, il est suffisant de n'allouer de mémoire que pour certains résultats intermédiaires. Lorsque les dépendances entre les calculs du programme sont dites uniformes, les données à allouer sont contenues dans les faces des tuiles voisines, dans une enveloppe rectangulaire de taille bornée et déterminable à la compilation. En choisissant de découper cette enveloppe en sous-enveloppes rectangulaires par projection, on obtient des ensembles de données qu'il est possible d'allouer en mémoire de manière contigue.

La connaissance du flot de données permet de connaître chacun des blocs à rechercher; on exploite alors le voisinage de ces blocs en mémoire, s'il existe, pour regrouper ensemble les accès aux différents blocs et obtenir les transactions les plus longues possibles. Ces deux niveaux de contiguité permettent d'obtenir une augmentation de la bande passante utilisée; les expériences qui ont été menées pour valider cette approche montrent qu'il est

ainsi possible d'utiliser l'intégralité de la bande passante vers la mémoire de l'accélérateur FPGA.

# 1.3 Analyse et découpage du flot de données

Dans le chapitre 5, on s'intéresse au comportement mémoire des programmes pavés lorsque le pavage est composé d'hyperplans quelconques. On effectue pour cela une analyse plus précise du comportement des programmes admettant une représentation polyédrique. Chaque tuile a besoin de résultats intermédiaires calculés par d'autres tuiles voisines. Lorsque les dépendances entre les calculs sont *uniformes*, toutes les tuiles exhibent une empreinte d'accès similaire sur leurs voisines. On propose alors d'exploiter cette régularité et de découper les données transmises en groupes dotés de trois propriétés :

- Atomicité : La consommation d'un élément d'un groupe implique la consommation de l'ensemble du groupe;

- Unicité de l'origine (irredondance) : aucun élément ne peut faire partie de plusieurs groupes à la fois, et chaque groupe est originaire d'une unique tuile.

- Maximalité : Si deux éléments ont exactement les mêmes tuiles consommatrices, alors ils appartiennent au même groupe.

Ces trois propriétés caractérisent, et permettent de construire, les MARS (Maximal Atomic irRedundant Sets) qui peuvent être utilisés pour, outre la construction d'une allocation de mémoire, la détection et la correction des erreurs.

# 1.4 Allocation de données partitionnée et compression à la volée

Dans le chapitre 6, on étudie une application de l'analyse précédente afin de construire une allocation de mémoire qui permette d'avoir l'utilisation la plus efficace du bus mémoire tout en y faisant passer le volume de données le plus petit possible. Il est ainsi nécessaire d'avoir recours à la fois à la contiguité et à la compression des données.

Les propriétés des MARS permettent d'exhiber des blocs contigus, candidats à la compression en raison de leur propriété d'atomicité; afin de maximiser la contiguité, il est nécessaire de l'étendre à travers les blocs MARS ainsi créés. On formule un problème d'optimisation pour disposer en mémoire les MARS en cherchant à minimiser le nombre d'accès burst effectués. On propose également de compresser les données des MARS, et d'empaqueter les blocs compressés pour gagner à la fois en bande passante et en données. Cela permet de travailler avec des données dont le type et la largeur sont arbitraires, ce qui est courant sur FPGA, sans perte de bande passante.

On implémente un générateur de code permettant d'automatiser la création d'unités mémoires spécifiques, exploitant les MARS et leur compression, pour des accélérateurs FPGA.

## 1.5 Extension aux dépendances affines

Dans le chapitre 7, on s'intéresse aux limites des méthodes proposées aux deux chapitres précédents. Ceux-ci ne peuvent considérer que les dépendances entre les calculs lorsque celles-ci sont *uniformes*. Sont exclus les accès à la mémoire issus de dépendances non-uniformes, qui constituent pourtant l'essentiel des accès de certains programmes.

Le modèle polyédrique permet de représenter des dépendances affines, dont celles uniformes sont un cas particulier. Dans ce chapitre, on étudie ainsi la forme des dépendances affines qui peuvent engendrer des structures similaires aux MARS, tant sur des espaces de données d'entrée, que sur des espaces d'itérations pour le passage de résultats intermédiaires. Il est nécessaire que soit préservée l'uniformité des ensembles de données consommés par chaque tuile, c'est-à-dire la forme et la position de chaque ensemble, pour les qualifier de MARS.

Il ressort de cette étude que peuvent amener à des MARS les dépendances affines uniques, ou celles multiples partageant la même partie linéaire ou, à défaut, le même noyau. On propose également une méthode construction des MARS dans ces cas. Le cas des dépendances entre espaces d'itérations déjà tuilés est étudié, et une conjecture sur l'existence de MARS est établie. Cette conjecture soumet l'existence de MARS dans l'espace producteur, à l'existence d'un lien entre un déplacement dans l'espace consommateur et un déplacement dans l'espace producteur.

# Chapter 2

# Introduction

Performance optimization is a major topic of computer science today. The continued demand for performance drives the emergence of domain-specific hardware accelerators, under the form of fully application-specific integrated circuits (ASICs), accelerators implemented inside configurable chips (field-programmable gate arrays, FPGAs), or also as specialized units within general-purpose processors.

Creating domain-specific hardware is not sufficient to get a high performance; the hardware must be fully exploitable and exploited. To this aim, hardware and software developers have to respectively provide and uncover parallelism, and correctly exploit the memory hierarchy. While general-purpose processors feature caches, dedicated accelerators instead rely on carefully-tuned memory management as well as on-chip and off-chip data movement. In both cases, it is up to the hardware designers and application developers to make the best usage of bandwidth: they must seek to use every cycle to transfer useful data on the memory interface.

Compilers have largely improved over the 2010 decade in terms of both automatic parallelism extraction and cache utilization. In particular, they have control over the *memory access pattern*, which is the sequence of memory accesses performed by the accelerator. By leveraging value reutilization, they reduce the volume of data transiting through the memory hierarchy. This is not sufficient to get the best performance out of the memory subsystem. Designers and developers still have to manually perform *memory allocation*, that is, specifying where (physical chip, bank) and in which order (layout) the data used by their accelerator is stored. A good data layout has a significant impact on performance: it makes it possible to get contiguous, regular access patterns, leveraging the highest performance out of caches, prefetchers and controllers.

Memory architectures are also evolving and diversifying: high-performance computers are moving away from a central memory of a single type, to multiple memory chips close to the processing units, each with its own bandwidth and random access latency. The performance of a certain program depends on its utilization of the specific type of memory available and the memory architecture.

Tuning the data layout in memory has been known to improve performance of numerous programs, but remains a difficult problem to this day. Purpose-built layouts for specific applications exist, but automation is desirable. In this document, we propose generic memory layouts that improve bandwidth utilization, and automatically derive such layouts from the programs themselves using compiler analyses.

This chapter motivates and gives an overview of this Ph.D dissertation. Section 2.1 details and motivates the specific problems that are solved in this document; Section 2.2 gives an overview of the solutions proposed.

## 2.1 A need for further memory optimizations

In this section, we explain the continued necessity of optimizing memory accesses. While there is an immediate challenge caused by the continued increase in pressure on memory due to more parallelism being exploited, there is a long-term challenge posed by the widening of the space of memory architectures. New memory architectures will be under-utilized unless the data layout and access pattern are carefully tailored to them.

The next two subsections detail this argument; Sections 2.1.3 and 2.1.5 focus on the specific problems caused by data layout and access patterns.

## 2.1.1 An increasing pressure on memory due to parallelism

Processor chips keep containing more logic cells, mainly due to progresses in silicon manufacturing. Thanks to these area gains, more computation units can be put in the same silicon space. These units are designed to operate in parallel; in order to get the best performance from this silicon, a program needs to fully exploit its compute units, and must therefore *exhibit* parallelism.

#### New hardware is massively parallel

Current architectures leverage multiple levels of parallelism, from low-level vector operations to high-level parallel nodes in a machine cluster.

On CPU and GPU platforms, the parallel computation units are grouped in vector units, that can perform the same instruction on multiple operands. This model is called Single-Instruction, Multiple Data (SIMD). On FPGA and ASIC designs, parallel computation units are explicitly specified, and it is the job of the hardware developer to ensure that all processing units and memories can be actively used at all times. Large-scale systems feature many of these chips that all run in parallel, which adds another layer of parallelism to exploit, and more parallelism to be exhibited by the program.

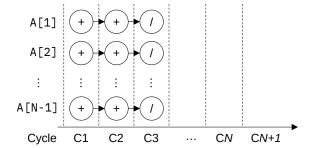

Hardware designers also have optimizing compilers at their disposal called *high-level synthesis* (HLS) engines. These transform imperative code like that executed on CPU or GPU into a hardware architecture; in doing so, they also rely on parallelism extraction techniques. Section 3.3 covers some of their specific optimizations to produce parallel hardware. Deriving a parallel architecture and fully utilizing it are two interdependent challenges; there is active research on HLS tools with respect to scheduling and resource sharing ([44, 60, 82, 87]...).

#### Auto-parallelization increases memory pressure

Automatic extraction of parallelism has significantly evolved thanks to active and continued research for more than 30 years; such automation reduces the burden on the developer, who no longer has to explicitly state where the parallel computations can happen in the program. A series of *optimization passes* exist in this regard.

Optimizers and frameworks exist to leverage various levels of parallelism:

• Data-level parallelism: loop vectorization, which has been part of state-of-the-art compilers for years [6] and usually makes parallel computations in a loop explicitly appear.

Superword-level parallelism extraction [46] can group together isomorphic, parallel operations and issue a vector instruction for them.

- Instruction-level parallelism: a superscalar CPU can execute multiple instructions in parallel in its various execution units. Part of this parallelization task is done in out-of-order CPUs by the re-order buffers (ROB), provided they can find independent, non-conflicting instructions in the program. Compilers can also re-order instructions to extract ILP; this is especially used for in-order processors, like very-long instruction word (VLIW) processors ([59]).

- Thread-level parallelism: Loop tiling [41], on top of reducing memory accesses of a program by making it cache-friendly, gives coarse-grain parallel workloads implementable as parallel threads. Calls to OpenMP make it easy to exploit the parallelism leveraged by tiling.

The exploitation of each level of parallelism increases the memory traffic. To process more operands at a time, the processor needs to get these operands from its memory hierarchy, which must in turn handle all this extra traffic without becoming a bottleneck. When this happens, the design is said to be *memory-bound*.

## 2.1.2 A widening space of memory architectures

#### New workload-specific memory technologies

Memories have intrinsic characteristics: access latency, bandwidth and capacity. How each system is manufactured determines these three parameters, that are in a tradeoff: a high bandwidth requires parallel access to a large number of data, and therefore a partitioning of the data within the memory. Partitioning increases the random access latency due to additional arbitration and multiplexing. Higher capacities also increase the multiplexing needs, and in turn the latency.

**Table 2.1:** Benchmark figures of various memory technologies (DDR4, HBM) and platforms (U280 board, Amazon F1 datacenter platform).

| Technology         | Bandwidth          | Latency | Capacity      | Usage              |

|--------------------|--------------------|---------|---------------|--------------------|

| U280 DDR4 [52]     | 38  GB/s           | 110 ns  | 32 GB         | Main memory        |

| Amazon F1 DDR [15] | $57~\mathrm{GB/s}$ | 561  ns | Variable (GB) | Accelerator memory |

| U280 HBM [52]      | 612  GB/s          | 108  ns | 8  GB         | Accelerator memory |

Each component in a system has its own bandwidth and latency requirements: for instance, CPUs tend to perform random accesses and need low access latency, while GPUs tend to perform regular access patterns and need a higher bandwidth. To cope with all these usages, a wide variety of memory technologies are simultaneously being developed. Table 2.1 shows benchmark results on various platforms using different memory technologies; latency, bandwidth and capacity can significantly vary from one platform and memory technology to another.

In order to get the best performance from these memory chips, how the programs use memory has to be tailored to the chosen technology.

#### More complex memory subsystems

Memory chips are generally part of a memory subsystem so that various components can access them. Central memory subsystems are among the most commonly implemented: a machine has a central memory all of its components (e.g., CPU, GPUs, daughter accelerator cards) can use, with a high latency, low bandwidth and high capacity. The pressure on such central memories and their limited bandwidth cause contention, hindering application performance.

Historically, caches and prefetchers have reduced the pressure on central memories; these features are private to each chip, and fail to address the contention issue where multiple accelerators exist, for instance in Systems-on-a-Chip (SoCs).

Distributed, networked memory subsystems are being developed to increase the overall bandwidth and relieve contention, in both small-scale systems (network on chip, NoC) and large-scale systems (software-controlled memory accesses).

On top of those challenges posed by individual memories, complex systems add a placement problem: accessing a random location in a complex subsystem has a high latency cost, even more so if the data is in a remote node of a distributed memory system. Adapting the placement of data within the subsystem becomes crucrial to get performance.

#### 2.1.3 Bandwidth-bound FPGA accelerators

On current architectures, the literature contains a significant number of references to bandwidth-boundness, particularly regarding FPGA accelerators. Two main memory subsystems surround FPGA accelerators today: DDR memories, shared with the rest of a System-on-a-Chip such as *Xilinx Zynq*; and the newer high-bandwidth memories, mostly available on high-end FPGA boards.

Cong et al. [19] evaluated DDR-based FPGAs and Graphics Processing Units (GPUs) by means of a benchmark suite called Rodinia, and bandwidth appeared to be a bottleneck on most tested benchmarks; an increase in available bandwidth to that promised by High-Bandwidth Memory (HBM), provided it is exploited, would lead to three FPGA benchmarks surpassing GPU at a better performance per watt ratio.

Some applications are intrinsically bandwidth-bound because they expose little reuse of their input data. This is the case of matrix-vector multiplication, used for instance in the fully connected layers of convolutional neural networks. Each element of the matrix is only used once, and therefore this application is known to be memory-bound on recent DDR-based FPGA platforms: in 2019, design space exploration for the Caffeine framework [86] to optimize the convolution part of a neural network on FPGA, resulted in the observation that all designs proposed by the framework would be bandwidth-bound. Acceleration of SpMV on FPGA is still an issue in 2023 [48], calling to a full utilization of the bandwidth by exploiting sparsity and data compression.

High-Bandwidth Memory is available in off-the-shelf FPGA boards such as Xilinx Alveo U280. While HBM increases the available bandwidth, it does not increase its utilization

unless data is spread over all banks. HiSparse [26] is an instance of FPGA accelerator class for matrix-vector multiplication where such a partitioning is performed. Microbenchmarks [52] show that a single HBM bank can reach about 14 GB/s whereas multiple banks can give a 421 GB/s bandwidth. This underlines the need for an automated data layout and placement.

# 2.1.4 Recent improvements in the utilization of memory subsystems

When memory access is the bottleneck, all the available parallelism cannot be exploited. To relieve this, the program must be optimized with multiple respects:

- Improving the access locality, re-utilizing values already on chip and reducing memory accesses,

- Fully utilizing the memory subsystem when accesses are needed:

- Avoiding cache misses: the memory accesses must re-use recently accessed addresses,

- Using prefetchers: the sequence of accesses must be regular enough to be recognized by the prefetching mechanisms,

- Exploiting the burst feature of memory buses: the addresses being accessed must be adjacent to each other.

Compiler passes have been developed to automatically address the above issues. This section gives a broad view of the optimizations they brought.

#### Improving the access locality

The first key to improving memory performance is to reduce the number of memory accesses, thereby improving the program's arithmetic intensity (AI) [78, 80]. Other ways to describe this in the literature are improving locality or reducing the reuse distance, with a

common idea that the closer in time the multiple accesses to a value, the more likely it is to stay on chip registers or be present in a closer cache level.

Well-known locality optimizations promote memory to registers [53] and re-order instructions to re-use values freshly computed instead of sending them to memory. Value reutilization is a key component of major production compilers such as GCC or LLVM today. On FPGA accelerators, it is the developer's task to specify which data movements must take place as synthesis tools do not promote memory accesses to registers. The work of Wei et al. [77] is an instance of deep neural network where memory accesses are saved by keeping some intermediate results on chip. This approach involves partitioning the results with knowledge of the consumers of the intermediate results. One of the approaches in this Ph.D dissertation automatically computes such a partitioning and can be used for this purpose.

More advanced locality optimizations target caches. Loop tiling [41, 45] is one of them: it aims at breaking up a loop nest into atomic blocks that have a known memory footprint, typically the size of some level of cache. It is possibly applied at multiple levels [92], from registers [42, 43] all the way to parallel nodes. It is applicable and can be profitable on CPUs as well as GPUs [36]. Although tiling can be applied purely as a loop transformation, it changes the execution order within the loop nest. Prior analysis, possibly automated [11, 12] must assert that it is legal, and profitable. Section 3.4.3 covers tiling in more detail using the polyhedral representation of a program. Tiling has made its way into production compilers; it is notably implemented in Polly [33] part of the LLVM optimizing compiler. Cache behavior is well-known, to the point it is possible to model and tune programs based on analytical cache miss equations [32].

#### Improving access patterns

Locality optimizations determine *which* addresses (containing which values) will be accessed at a certain point in time. Re-ordering these accesses can exhibit regularity in the address sequence and yield better performance.

Regular access patterns enable usage of prefetchers and contiguous access patterns (more restrictive than regular) enable the use of burst features, both improving performance. Prefetcher-friendliness optimizations notably try to expose regularity in the memory accesses that can be identified by the prefetcher.

Burst-friendliness is generally not an issue on CPUs and GPUs because the granularity of memory accesses is at least a cache line. Therefore, burst-friendliness is a problem mostly for FPGA and ASIC designs. Nevertheless, the fundamental issue at stake is not FPGA-specific: data contiguity is necessary to get good vector unit performance. Auto-vectorizing compiler passes such as superword-level parallelism (SLP) [46] extractors required such data to be contiguous, as data movement or shuffling within vector registers incurs an overhead that could lead to a slower code despite vectorization. More recent SLP extractors [49] can change the data layout if the accesses are regular enough, e.g. with a constant stride. It is also possible to re-order accesses within a DDR controller itself to exhibit bursts, and reduce the access latency seen from the outside of the controller [20].

The optimizations above do not guarantee the absence of cache misses, burst- or prefetcherfriendliness: how the data is laid out in memory can prevent the appearance of regular or contiguous access patterns. The next subsection deals with the specific issue of data layout.

# 2.1.5 Application-specific data layouts increase bandwidth utilization

A raison d'être of this Ph.D dissertation is that the choice of data layout in memory affects memory access performance. As said in Section 2.1.3, irregular and non-contiguous accesses prevent correct utilization of prefetchers, of auto-vectorizers but also cause high-latency scalar accesses on global memories.

There have been various attempts at modifying the memory layout that resulted in performance improvements. We give examples of them in the next subsections, and make the case that actually generalizing and automating them is a contribution towards fully utilizing current and future architectures.

#### Domain-specific layouts for FPGA accelerators

Due to the massive parallelism FPGAs offer, they are prone to memory-boundness. The literature contains a wide variety of methods to fully exploit the bandwidth of memories connected to FPGA accelerators. They mainly rely on increasing spatial locality by exhibiting data contiguity, which this dissertation largely covers. How this is achieved depends on the application, of which two examples are given below.

One way to exploit memory contiguity is to build streams of data, where the order of writing of the data is the same as the order of reading. It is possible thanks to works like SODA [13], to get such layouts for FPGA accelerators of applications like dense linear algebra or stencils.

An application that benefits from domain-specific layout is sparse matrix-vector product. On top of exploiting sparsity to compress the matrix data, further optimization is done with the layout of the compressed data, yielding a higher bandwidth utilization. It is possible, like done in HiSparse [26], to partition the data to match HBM banks, thereby exploiting all the banks of an HBM stack.

#### Fine-grain data layouts for vectorization

The works presented in this dissertation target domain-specific hardware accelerators. Yet, the problem being tackled is more general. It is for instance possible to improve the performance of instruction-set architectures in certain scenarios, such as vectorized programs, by using specific data layouts.

Vectorization is exploitation of a chip's vector units instead of equivalent scalar operations. It is achieved by using special instructions of the processor. Such instructions typically consist in replicating a single operation over multiple operands, ("single-instruction multipledata", SIMD). While vectorization helps in improving compute unit utilization, it requires careful data placement to limit the movement from, to and within vector registers. Solutions to this problem exist for domain-specific applications; for instance, for stencil computations, a specific data layout for the vector registers, distinct from that of the original arrays, can reduce the overall data movement from/to and within the vector registers [83].

#### 2.1.6 The case for automation of memory layout optimizations

We make the case that memory layout optimizations should be made automatic, for the same reason as other performance optimizations. Such optimizations are hard to write by hand and, although nothing prevents the developer from applying manual optimizations, compiler-based ones provide:

- "speed": what would take a few hours or days for a human to design just takes seconds (e.g., manual RTL design is orders of magnitude more time-consuming than HLS).

- explorability: it is posssible to automatically generate a wide variety of designs, evaluate them and pick the best one.

- applicability: a single compiler pass can generate a memory allocation, possibly using target-dependent cost models but using the same optimizer code, and target-dependent backends generate all the data movement code necessary to use an allocation.

How to automate the derivation of a good memory layout is an issue in itself. Compilers can syntactically invert the dimensions of memory arrays using cost metrics [69]. Syntactic manipulations may however not be sufficient; Polyhedral optimizers can produce complex domains such as diamond tiles [9], and likewise complex access patterns, for which a complete re-engineering of the memory layout is needed to obtain good memory performance.

In this dissertation, we propose to use the polyhedral representation of programs to build memory layouts and propose algorithms and systematic methods to compute memory layouts. These techniques will work provided a certain number of hypotheses, determined for each technique, are verified.

### 2.2 Contributions of this Ph.D

We have made the case for the necessity of automated memory layout optimizations. Most of the contributions of this Ph.D. rely on one idea: like prior work generates parallel code from the polyhedral representation of a program, it is possible to generate contiguous memory layouts from the same polyhedral representation. Such contiguous layouts enable domain-specific hardware accelerators to have a high bandwidth utilization.

Chapter 3 covers the technical background all of this document relies upon; Chapters 4 through 7 cover the solutions proposed by this Ph.D, of which a brief summary is given below. They are described below, from the most restrictive scope of application to the least restrictive.

### 2.2.1 A multi-level contiguous memory layout for rectangular tiles

In Chapter 4, we focus on **programs tiled with a hyper-rectangular tile shape** and that have *uniform dependences*. For these applications, we can compute the *flow-in* and *flow-out* data as parts of thick faces, called "facets", of neighboring tiles. Therefore, we allocate data for these facets in such a way to enable contiguity within them and across them. These two levels of contiguity enable long burst accesses that result in a high bandwidth utilization, while keeping and a low redundancy. This allocation scheme is called Canonical Facet Allocation (CFA).

We propose an evaluation of this allocation scheme with an FPGA implementation of benchmark accelerators as task-level pipelines. For these, the external I/O phases (off-chip CFA from/to on-chip allocation) are generated using a compiler pass, and show that we are able to reach close to bus bandwidth.

# 2.2.2 An irredundant, atomic partitioning of inter-tile communications for arbitrary tile shapes

In Chapter 5, we consider **programs tiled with arbitrary shapes**, rather than rectangles as required by Chapter 4. Based on the observation that only a part of the flow-out of each tile is used by every of its consumer tiles, we proposes a **breakup of these flow-in and flow-out sets** that guarantees atomicity and irredundancy properties, and a method to construct such a breakup. The resulting sets, called Maximal Atomic irRedundant Sets (MARS), can be used in a variety of applications among which memory allocation, but also error detection.

# 2.2.3 A compressed and contiguous memory layout for arbitrary tile shapes

Chapter 6 is a use case of the MARS: it introduces a memory allocation based on the MARS that exploits its irredundant and atomic natures. These two properties allow for contiguity, data packing and compression, thus increasing the bandwidth utilization and decreasing the volume of data. This chapter brings in two contributions: through an optimization problem, it exploits the MARS irredundancy to minimize the number of input and output transactions for each tile; and, the atomicity property is exploited by automatically compressing and packing the data. A code generator is implemented and the resulting allocation and access pattern are evaluated on a selection of FPGA accelerators.

# 2.2.4 An extension of the data flow partitioning to affine dependences

One limitation of MARS is that it does not apply to affine dependences, that make up most of the input data on workloads such as matrix multiplication. Chapter 7 extends the idea of atomic irredundant partitioning to data spaces with affine dependences. Affine dependences bearing several properties (notably sharing the same null space) can yield

such a decomposition; in this case, Chapter 7 proposes a method to partition the data into MARS. This chapter's theoretical contribution makes it possible to propose a data layout for the entire data flow with the same objectives as the one obtained in Chapter 6.

# Chapter 3

# Background

This dissertation relies on a fairly large stack of technical background: it uses both low-level hardware design techniques and high-level mathematical representations of programs. Between these, multiple levels of abstraction are involved and interact together. All of these levels of abstraction are necessary to efficiently use all the compute power of accelerators. This chapter aims at explaining the abstraction stack and giving design techniques related to memory accesses.

It first covers hardware memory architectures, their interfaces and controllers. It goes through the synthesis of compute and memory architectures from high-level code, then covers the high-level polyhedral abstractions used to analyze and transform the source program; finally, it explains how high-level transformations can have a controlled effect on low-level memory accesses.

## 3.1 Locality and performance

The performance of a program on a platform, i.e. how many computations it can perform per time unit, is determined by how the compute power of the platform and how the memory subsystem are utilized. In this dissertation, the focus is on the memory subsystem and locality optimizations; this section gives an insight into the effects of these optimizations on performance.

#### 3.1.1 Roofline model

Quantifying the performance of a program is necessary to determine which kind of optimizations are needed, i.e. where there is room left for performance gains.

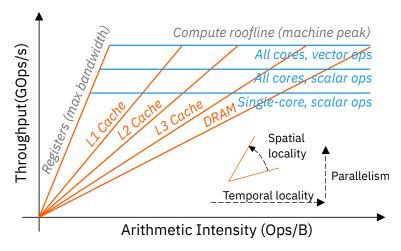

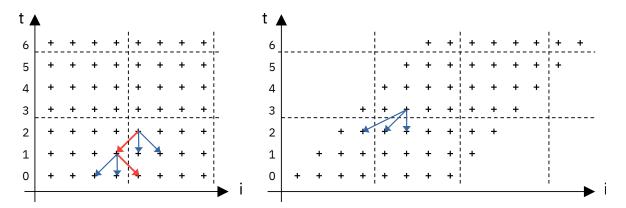

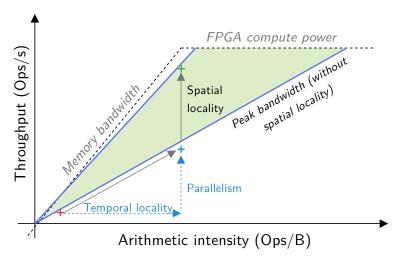

Figure 3.1: Roofline model

The roofline model [78, 80], illustrated on Figure 3.1 is a visual way to see the effects of locality improvements. The throughput a system can reach is bound when either a memory roofline or a compute roofline is hit. Compute rooflines represent the maximal throughput attainable with a given set of compute units; in the case of hardware designs, the maximum number of compute units that fit a given area budget are considered. Memory rooflines represent bandwidth caps intrinsic to the memory subsystem; there is one such roofline per level of the memory hierarchy.

To figure out the position of a program or hardware design in such a graph, one must compute its *arithmetic intensity* (AI), which is defined by:

$$AI = \frac{\text{number of arithmetic operations}}{\text{volume of I/O}}$$

A higher AI generally means a better achievable performance, thanks to a reduced likelihood of memory-boundness.

Memory-boundness results in an under-utilization of the on-chip parallel compute resources due to stalls; using a roofline graph, it is possible to explain how improving both spatial and temporal locality can relieve memory-boundness. The next subsection focuses on the two notions of spatial and temporal locality.

### 3.1.2 Access locality

The performance of memory accesses largely depends on how close together they are, in both time and space; correct utilization of the memory subsystem by improving the sequence of addresses in both time and space results in a good performance. There are two qualitative notions of locality used to characterize the utilization of the memory subsystem by a program or accelerator.

Temporal locality characterizes how close in time the same addresses are being re-used by the program with a re-use distance. The lower this distance, the more likely the data is to be in a close level of cache; if the reuse distance is low, the data may still be available in on-chip registers. Improving temporal locality reduces the number of global memory accesses, and therefore increases arithmetic intensity. As shown in Figure 3.1, a higher temporal locality gives potential access to higher compute performance by limiting the pressure on memory.

Spatial locality, on the other hand, characterizes how close in space consecutive addresses being accessed are. If addresses are all adjacent to each other, the program has better locality than if they are not. For instance, a unit-strided access sequence has better spatial locality than a two-strided sequence, because the latter sequence does not exhibit any contiguity. In Figure 3.1, the effect of spatial locality on performance can be seen as the bandwidth utilization increases, thereby giving access to more compute power for the same arithmetic intensity.

## 3.2 Memory architectures and transfers

A memory architecture usually encompasses the storage locations of all *active* data with the exclusion of cold data stored on disks. Such memories are of the following type:

• Disk, usually for swapping. These have low throughput (hundreds of MB/s for mechanical disks to 32 GB/s for PCIe SSDs), very high access latency (milliseconds) and very high capacity (terabytes);

- DDR random access memory. This is where the bulk of a system's memory resides. It is attached to the main processor system or is on some daughter card, e.g. a GPU. It has high throughput (up to 128 GB/s), low latency (below 1 microsecond) and low capacity (below 1 TB usually).

- HBM random access memory. These have very high throughput (more than 500 GB/s) and a higher access latency than DDR (up to a microsecond) due to extra arbitration, while being usually smaller than regular DDRs. These are used for high-throughput processing.

- Caches, that are embedded on CPU or GPU chips. These have low access latency

(nanoseconds) and low capacity due to the area they take and the expensive logic

needed to manage them.

- Registers, that are located right next to the compute units. These have the lowest latency (ideally same-cycle access) but are also the rarest storage resource. They are the only type of memory onto which operations are directly performed, barring compute-in-memory engines.

Registers are driven by the compute engines themselves, to which they belong. Other kinds of memories need controllers to be accessed.

## 3.2.1 High-bandwidth controller features

Memory controllers geared towards high bandwidth accesses feature ways to hide access latency of individual memory addresses, mainly by using some sort of pipelining. Burst-mode accesses and transaction-level pipelining are usually available; this subsection describes both features.

#### **Burst-mode transactions**

Memories are seldom dedicated to a single component, and are more usually connected to shared buses. Transaction-based shared buses require the use of two-way handshaking

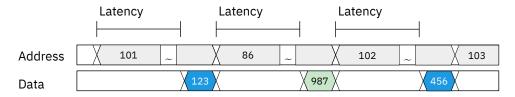

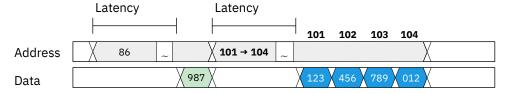

(a) Scalar access pattern: there is a latency between each data transfer.

(b) Burst access pattern: multiple values are retrieved from consecutive addresses (101 to 104), without latency between each value. There is still a latency between accesses (non-contiguous in this example).

**Figure 3.2:** Burst accesses span over multiple addresses in a single transaction, amortizing the transaction latency over all elements accessed.

protocols before data transfer can begin. Arbitration and access protocols ensure that there are no access conflicts. During this time, the data transfer unit on the accelerator side is idle, as between data transfers in Figure 3.2a.

To amortize the access latency, shared buses usually feature burst-mode accesses, which perform several back-to-back accesses at consecutive addresses, as illustrated in Figure 3.2b. In order to use this burst mode, the accelerator must know:

- how much data it needs to transfer,

- which address is the first one to be accessed.

In first approximation, the latency of such accesses is modelled as an affine function: to transfer  $N_{\text{words}}$ , the number of cycles will be:

$$t_{\rm burst}(N_{\rm words}) = t_{\rm handshake} + \frac{N_{\rm words}}{\rm words~per~cycle}$$

It is clear that the bigger  $N_{\text{words}}$  is, the lower the impact of  $t_{\text{handshake}}$  and the higher the bandwidth utilization.

It is possible to hide the latency caused by the handshake protocol by overlapping actual data transfers with subsequent requests. Such overlapping can be compared to a two-stage access pipelining, splitting requests and transfers. This feature is present in the AXI4 bus, and exploited by some high-level synthesis tools described in the next section. Notably, when the end of a burst is contiguous to the start of the next burst, the tools generally can schedule them in a pipeline.

# 3.3 High-level synthesis

Generating hardware is usually done at the register-transfer level (RTL). This level of abstraction is very low and it is very difficult to reconstruct the algorithm from an RTL representation. This prevents rapid exploration of the design space, and requires skilled engineers to build hardware devices.

Well-known languages in the computer science field are mostly imperative languages such as C or C++. These languages do express the *what* of the program, i.e. which operations should happen on which operands, and abstract away the *how* which is bit manipulations. RTL on the other hand expresses the *how* and does not contain the *what*. When we want to design a piece of hardware, we start from the algorithm and go down to the bitwise operations that it needs to execute.

High-level synthesis (HLS) consists in automating hardware synthesis from an imperative language, and generating RTL from this language. Commercial tools such as Vitis HLS and Catapult accept C and C++ code as input, mostly due to these languages being used in embedded systems development and well-known from the EDA field.

# 3.3.1 From C/C++ to an architecture